2017年云南農(nóng)業(yè)大學(xué)三大科學(xué)技術(shù)創(chuàng)新成果匯

2017年,云南農(nóng)業(yè)大學(xué)在科技創(chuàng)新方面取得了顯著成就,尤其在技術(shù)開發(fā)領(lǐng)域,形成了三大核心創(chuàng)新成果。這些成果不僅體現(xiàn)了學(xué)校在農(nóng)業(yè)科技研究中的領(lǐng)先地位,還推動了地方經(jīng)濟(jì)發(fā)展和產(chǎn)業(yè)升級。以下是三大科學(xué)技術(shù)創(chuàng)新的詳細(xì)匯總:

1. 作物新品種選育技術(shù)

云南農(nóng)業(yè)大學(xué)在作物遺傳改良領(lǐng)域取得了突破性進(jìn)展,通過分子標(biāo)記輔助育種和基因編輯技術(shù),成功選育出多個高產(chǎn)、抗逆的新品種,如耐旱水稻和抗病玉米。這些品種在云南及周邊地區(qū)推廣種植,顯著提高了糧食產(chǎn)量和農(nóng)民收入,同時減少了農(nóng)藥使用,促進(jìn)了可持續(xù)農(nóng)業(yè)的發(fā)展。

2. 農(nóng)產(chǎn)品加工與保鮮技術(shù)

學(xué)校在農(nóng)產(chǎn)品加工領(lǐng)域開發(fā)了多項創(chuàng)新技術(shù),包括新型干燥、發(fā)酵和包裝方法。例如,研發(fā)的低溫真空干燥技術(shù)有效保留了水果和蔬菜的營養(yǎng)成分,延長了貨架期;同時,利用微生物發(fā)酵技術(shù)開發(fā)了功能性食品,如益生菌飲料,提升了農(nóng)產(chǎn)品的附加值。這些技術(shù)已與企業(yè)合作產(chǎn)業(yè)化,帶動了當(dāng)?shù)剞r(nóng)產(chǎn)品加工業(yè)的轉(zhuǎn)型升級。

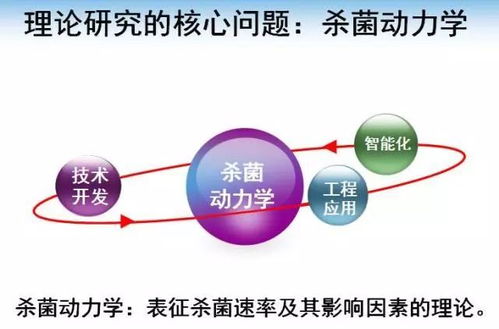

3. 農(nóng)業(yè)信息化與智能裝備技術(shù)

云南農(nóng)業(yè)大學(xué)結(jié)合物聯(lián)網(wǎng)和大數(shù)據(jù)技術(shù),開發(fā)了智能農(nóng)業(yè)管理系統(tǒng),實現(xiàn)了作物生長環(huán)境的實時監(jiān)測與精準(zhǔn)調(diào)控。配套研發(fā)的智能灌溉、施肥裝備,通過傳感器和自動化控制,優(yōu)化了資源利用效率,降低了生產(chǎn)成本。這一創(chuàng)新不僅提升了農(nóng)業(yè)生產(chǎn)智能化水平,還為鄉(xiāng)村振興戰(zhàn)略提供了技術(shù)支撐。

總體而言,2017年云南農(nóng)業(yè)大學(xué)的三大科技創(chuàng)新成果在技術(shù)開發(fā)方面展現(xiàn)了強(qiáng)大的研發(fā)實力,為農(nóng)業(yè)現(xiàn)代化和區(qū)域可持續(xù)發(fā)展作出了重要貢獻(xiàn)。未來,學(xué)校將繼續(xù)深化產(chǎn)學(xué)研合作,推動科技成果轉(zhuǎn)化,服務(wù)國家戰(zhàn)略需求。

如若轉(zhuǎn)載,請注明出處:http://m.zcrskj.cn/product/17.html

更新時間:2026-04-28 02:43:21